英特尔、AMD下一代处理器架构解析

没错,英特尔、AMD又到了产品升级换代的时候了。英特尔的Tick-Tock到了Tock这一步,新产品Haswell箭在弦上;AMD虽然暂时落后一局,但新的压路机也是曙光在前,蓄势待发。那么,究竟Haswell和压路机都有哪些改进?英特尔和AMD的竞争又会开发出哪些新技术呢?本文将带你提前了解英特尔和AMD的下一代处理器架构。

Haswell——小改进,大步伐

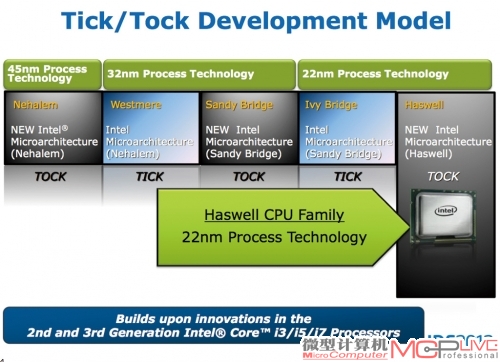

从英特尔发布了基于Core Microarchitecture(酷睿微架构)的Core 2 Duo系列到现在,英特尔对处理器内部核心架构的改进并不算大。从Core 2 Duo,到Nehalem Core i7,然后到Westmere、Sandy Bridge直到今天的Ivy Bridge,CPU微架构都可以算作是酷睿微架构的继承和发展,更多的变化则是工艺、总线、缓存等外围部件。在Ivy Bridge后,英特尔执行的是“Tick-Tock”中的“Tock”战略,这意味着Ivy Bridge的继承人“Haswell”所面对的目标是“使用成熟工艺,升级CPU架构”。除了处理器外,Haswell处理器将搭配代号为Lynx Point的主板芯片组,组成Shark Bay计算平台。

Haswell属于Tock部分,工艺不变(实际上也升级了),架构进步。

从目前掌握的消息来看,Haswell相比Sandy Bridge来说,在CPU架构方面改进大的当属加入了新的、有利于多线程执行的TSX扩展,以及大幅度提升整数计算性能的AVX 2.0技术。除此之外,Haswell在工艺方面也有所改进,当然CPU内部一些组件也会做出微小调整,但对整个CPU架构的影响不大。另外,在集成图形处理器方面,Haswell的图形性能会有比较明显的增长,EU单元数量会增加,功能上会进一步支持Direct X11. 1。在结构和扩展性能方面,Haswell在接口、封装模式上会做出一系列改动,CPU内部集成的电压控制单元会有改进,芯片组方面会采用更新的8系列芯片组。对玩家的一个好消息是,Haswell有望实现一定幅度的自由超外频。

TSX和AVX 2.0进驻——Haswell的CPU架构改进

Haswell的CPU架构改进主要集中在对CPU应用的改进上,本身硬件基础如传统的四发射设计、分支预测、内存控制器、缓存设计等部分的改进都比较小。因此本文的介绍重点也会集中在Haswell新增的TSX和AVX 2.0功能上。

可用、安全的细粒度线程锁定——TSX扩展

说起TSX的功能,先要从CPU超线程技术讲起。CPU超线程技术的主要目的是在CPU的一个处理核心中,同时运行多个线程。这项技术的思想来源甚至可以追溯到上个世纪90年代的“指令并行化”思想。

从技术发展的角度来看,类似“指令并行化”在发展过程中出现了诸如粗粒度多线程(Coarse-Grained Multi-Threading)、细粒度多线程(Fine-Grained Multi-Threading)和同步多线程(Simultaneous Multi-Threading)等多种方式,这些方式各有特色,也各有优劣。

所谓粗粒度多线程,是指在单一线程操作过程中,如果遇到某线程长时间延迟,那么立刻将此线程锁定并切换到另一线程,执行完后再切换回来。举个例子来说,粗粒度多线程类似于如下情况:在公用服务器上有一个文件夹,里面有100个文件。当A用户修改文件夹中任何一个文件时,整个文件夹会被锁定并进入只读状态,当B用户要访问文件夹时,他只能读取、复制文件夹内的文件,但无法修改。

粗粒度多线程是相当容易实现的一种多线程方案。这种方案的优势在于控制起来很简单,不容易出现冲突,但相对来说,粗粒度多线程“竞争损耗”比较大。所谓“竞争损耗”是指多个并行线程由于锁定等问题,终并行化不理想,操作中串行化大于并行化,终带来的性能增益很微小。

为了解决这个问题,细粒度多线程开始出现。它是指在每个时钟周期内,多个线程并行切换操作。依旧使用上文的例子来解释细粒度多线程:公用服务器上的文件夹中有100个文件,A修改文件夹的0号文件时,其余的99个文件并不会被锁定,B如果想修改3号文件,依旧可以自行修改。这样的锁定“粒度”相比之前的案例要小很多,可以锁定发生在更为细微的单个文件上,而不是整个文件夹。

细粒度多线程相比粗粒度多线程,对线程的控制更为细致,理论上并行度更好,但实际上细粒度多线程对程序的锁定更为细致,因此编程更为复杂,更容易出现错误和冲突。此外,细粒度多线程由于经常需要来回切换线程,每一次切换会浪费一定的时间,因此在单任务性能上细粒度多线程可能不如粗粒度多线程。总的来看,无论是细粒度还是粗粒度,都各自有优缺点,不能一概而论。

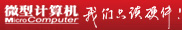

下面回归主题,目前处理器使用的多线程技术由于编程难度等问题,多使用粗粒度多线程,程序员只要在多个线程有可能冲突时直接锁定某线程即可。但这种粗粒度多线程在当前的应用环境下对性能提升的帮助有限,特别是对CPU多线程性能提升不大。实际上早在IDF 2006上,英特尔提出未来的处理器将使用事务型内存(Transactional Memory)和一些扩展技术来加强多线程的性能。所谓事务型内存,英特尔在这里应该并非是指物理内存或者与之相配的硬件设计要做出重大变化,而是指在程序编制过程中内存控制和使用的方法要改进为事务型内存的所代表的方法,也就是软事务型内存,其主要内容是原子对象和冲突判决器。简单来说,事务型内存的作用是针对不同事务(可以简单理解为线程)处理进行判断和沟通,并且在事务出错时能够回到之前的状态,从而在多任务并行处理时尽量避免发生错误。

在提出事物型内存后,英特尔又发布了一篇名为“Transactional Synchronization in Haswell”的文章,介绍了下一代Haswell上即将使用的TSX扩展。TSX的作用很明确,就是搭配事务型内存使用,为未来的CPU提供更强大的多线程能力。英特尔认为,在使用了事务型内存、并采用了TSX扩展后,TSX扩展能够自动判断、评估软硬件的情况。在使用细粒度线程锁时,TSX扩展能够帮助程序员实现更为简单、准确的无错细粒度线程锁。根据英特尔数据,在使用了事务型内存和TSX扩展后,部分锁操作的性能可提升1~3倍。在软件仿真中,比如事务型内存锁操作只需要4.6秒,而传统内存需要高达10.6秒,性能提升显而易见。

当然,采用TSX扩展后,性能提升并非马上体现。TSX扩展的应用场合和内容都比较复杂,需要软件、硬件的全面配合,并且目前的软件基本上不会在TSX扩展中带来明显的性能增益。只有那些符合英特尔要求的软件,才能在多线程应用中有相当明显的、相对于传统编程方法的性能提升,这属于软件普及和应用的道路问题,还相当漫长。

整数和浮点性能继续提升——AVX 2.0

AVX是Advanced Vector Extensions高级矢量扩展的简写,AVX在之前的Sandy Bridge和Ivy Bridge上就已经开始使用。目前的AVX指令集主要是用于增强浮点计算性能,它使用了256bit SIMD浮点指令集,支持三位数和四位数操作,也支持VEX编码方式。新的256bit浮点计算以及各种特色功能等相比前代的128bit有了巨大提升,在理想的情况下,256bit一次可以读更多的指令,浮点性能高提升可以达到128bit的2倍。另外,目前的新软件也开始使用AVX指令集来提升浮点计算能力,增强计算效能。

Haswell的芯片面积并不大,图为早前流传出的Haswell对比Ivy Bridge、Sandy Bridge等处理器的核心晶片。

在新的AVX 2.0中,英特尔也将整数计算部分升级到256bit SIMD阵列,CPU的整数计算性能得到大幅度提高,此外还添加了一些新的指令用于继续加强浮点性能。之前Sandy Bridge和Ivy Bridge不支持的FMA浮点乘积累(Floating Point Multiply Accumulate),在Haswell中终于给予支持。不过英特尔支持的FMA指令依旧是FMA3,AMD则更进一步支持FMA4(FMA4相比FMA3,除了在数据格式要求上更为灵活一些外,和FMA3相比只是一种计算的两个方面而已,并非换代性技术)。不过英特尔则认为FMA3已经能够提供更高的峰值速度,在高性能计算、图形处理等计算中有不错效果。

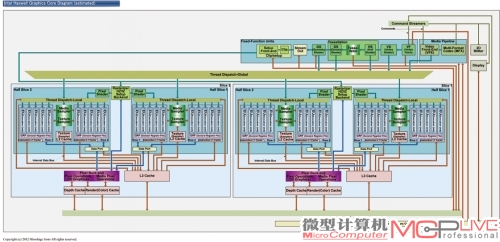

业内人士根据英特尔公布的Hawell的GPU部分架构图画出的详细架构内容,相比Ivy Bridge的GPU部分基本没太大变化。

AVX 2.0除了256bit整数计算以及FMA指令的加入外,还额外增加了不少用于加强计算、降低编程难度和提高精度的指令集,比如任意到任意排列(Any-to-Any permutes)、矢量位移(Vector-Vector Shifts)、Gather/Scatter指令以及3操作数通用位处理指令(3-operand generalpurpose Bit manipulation instructions)等。这些指令的加入,使得CPU可以在数据压缩、大规模计算、图形处理中速度更快,对程序员来说,编程过程也可能由于新指令集的使用而更为简单轻松。根据英特尔的数据,AVX 2.0搭配Haswell(L1缓存带宽从前代的48Byte/cycle增加到Haswell的96Byte/cycle,L2从32Byte/cycle增加到64Byte/cycle)后,CPU的每个核心、每时钟周期的单精度和双精度浮点理论高性能翻了一番,每个核心、每时钟周期的计算能力分别达到了32FLOPs和16FLOPs。再考虑CPU的高频率和多核心,在浮点能力方面Haswell将继续大幅度前进。

更多亮点——封装规格、超频和功耗等

在CPU其余架构部分,比如桌面CPU的四个物理核心、环状总线、Turbo Boost加速、PCI-E 3.0支持以及双通道内存等,Haswell和上代Ivy Bridge基本没有差别。其余的一些参数,如接口等物理规格,Haswell相对前代产品还是做出了一定程度的更改。

Haswell处理器的桌面平台使用了新的Socket H3接口,针脚数量更改为1150个,支持35W~95W的散热解决方案。移动平台分为两部分,第一部分是Socket G3插槽,947针脚,依旧是双芯片封装,TDP范围是37W~47W之间,嵌入式产品会降低到15W;第二部分则是全新的单芯片SOC接口,TDP降低到15W。第二种SOC类型的单芯片封装是专门为超级本和一些对面积要求很严格的产品而设计的,因此玩家可能会看到基于Haswell的体积更小、更轻薄的移动设备上市。

Haswell还有特别值得注意的改进之处,那就是调压模块。现在的CPU中往往会集成不同的部分,比如CPU核心、缓存、北桥、I/O接口等。这些部件在工作时需要不同的电压输入,因此CPU中会涉及调压模块来调整、监控每个部分的电压、电流等情况。在Haswell之前的产品中,调压模块分为五大部分,分别针对PLL锁相环、处理器内核、图形内核、System Agent部分、I/O部分等分别调节。在Haswell上这五部分合为一体成为一个独立的输入VR,集成度更高。目前尚没有特别明确的消息说明调压模块和为一体后对超频时的电压控制有什么影响,不过和Haswell对超频略微友善的态度来看,至少不应该太过负面才是。

没错,Haswell对超频更为友善了。之前的Sandy Bridge和Ivy Bridge的外频几乎不能调节,倍频调节除了“K”系列产品外,其余产品都受到很大限制。在Haswell上,英特尔决定对超频特别是外频的控制稍稍放开,引入了之前在LGA 2011平台上所使用过的技术——时钟参考比率(Reference Clock Ratio)。Haswell外频被分为1.0、1.25和1.67三个级别,高外频可以达到167MHz,虽然对超频玩家来说,传统以“1MHz”为单位的超外频再也不会回来了,但至少Haswell有希望通过改变外频来提升频率。

Haswell的功耗也进一步下降,首先是工艺,Haswell的工艺依旧是22nm 3D晶体管。但由于工艺进步,Haswell的22nm工艺和Ivy Bridge相比显然要更为先进一些,英特尔没有具体说明改进在哪些方面,只是含混地说“工艺不断进步,产品设计也有了变化,晶体管分配自由度更高”等。其次则是具体功耗数值了,一些演示消息表示Haswell功耗可以降低到低7.5W的惊人程度,技术上自然有一定革新。英特尔为Haswell加入了一个24MH的超低Bask Clock,用于超低电压处理器节能。节能模式上也加入了更深度休眠、更低电压唤醒、更少组件运转的C8、C9、C10节能模式,甚至可以直接关闭除了电源和部分缓存外的其余所有部分,在不同的睡眠模式中切入切出的速度也多提升了25%,更有利于节约能源了。

规模更大的EU单元——Haswell的GPU改进

英特尔在图形性能上每一次产品革新都宣称大幅度提升性能,但实际产品的表现却依旧难以和同期的入门级独立显卡抗衡。除了驱动等一直以来都不占优势的部分外,英特尔在GPU硬件设计上的弱势也是非常重要的原因之一。不过好在Ivy Bridge的GPU部分终于在硬件架构上支持了DirectX 11,也加入了一个曲面细分单元,算是完成了DirectX 11的所有功能支持。相比AMD和NVIDIA比拼抗锯齿技术、比拼通用计算性能,英特尔暂时还处在“是否跑得起来不重要,有没有才是关键”的层次上。

由于Ivy Bridge的GPU部分设计还算比较合理,因此Haswell的架构没有大规模改动,反倒是开始进行横向的规模扩张。根据英特尔的介绍,Haswell的GPU部分和CPU完全捆绑在环形总线上,可以使用L3缓存,并且GPU和CPU部分的TDP可以做到动态调整。一般情况下GPU和CPU不会同时满载,GPU很忙碌的时候CPU往往都是在等待GPU传回处理数据,因此Haswell可能会让GPU和CPU频率、功耗在更大范围内联动。这样能够在TDP允许的范围内获得更为优秀的图形性能。此外,Haswell还改进了GPU的纹理采样性能,高可提升4倍,这种改进在目前高清晰纹理普遍使用的情况下非常有用。

至于GPU规格方面,英特尔确认了三种版本,GT1、GT2和GT3。从英特尔给出的消息来看,GT2的规格可能是GT1的两倍、GT3则是GT2的两倍。不过GT3仅仅用于移动设备,桌面CPU只有GT1和GT2两个版本。根据业内一些消息,每个EU单元有4个ALU,GT1版本可能有6个或者10 个EU单元,总共就是24个或者40个ALU,1个曲面细分单元(之所以有两种猜测,是因为在Sandy Bridge和Ivy Bridge上,英特尔给GT1同档次的产品都只布置了6个EU单元,Haswell上也可能存在这样的情况,不过英特尔也有可能布置10个EU单元用于加强入门级产品的图形性能)。GT2则拥有20个EU单元,80个ALU和2个曲面细分单元,GT3则直接翻倍到40个EU单元、160个ALU单元和4个曲面细分单元。仅仅从ALU的数量来看,目前的入门级显卡比如NVIDIA的GK107核心,至少有384个ALU,而AMD的HD 7750也拥有512个ALU,Haswell的ALU数量上还是无法和入门级低端显卡抗衡,性能表现上自然不会太好了。

英特尔在图形性能上追求的是“ 功能型”产品,因此除了图形性能,传统属于显卡处理的视频方面,Haswell也有改进。首先是视频输出方面,Haswell的GPU支持DVI、HDMI 1.4a、Display Port 1.2、e-DisplayPort等新规格,视频输出能力方面有了保证。在视频的编、解码能力上,它支持JEPG、Motion JPEG(一种使用JPEG压缩帧的视频格式)、SVC(弹性视频编码)和MVC(多视角视频编码)等多种视频格式的解码。在视频处理上,Haswell的GPU拥有一些新的模块,比如伽玛扩展(GE)、肤色调节过滤器、帧率转换、图像稳定引擎等。

功能更多——全新的8系列芯片组

在本文一开始,曾提到过Haswell处理器的接口已经改变,目前的7系列主板已经不能继续支持Haswell处理器。Haswell处理器相搭配的是全新的英特尔8系列主板,芯片代号为Lynx Point。

英特尔表示Lynx Point在I/O接口、存储性能、安全性能以及管理性能方面都有颇多特色。安全性能和管理性能主要是商业用途,与普通玩家关系不大,比较有亮点的是I/O接口和存储性能。

首先来看I/O接口。Lynx Point对USB 3.0和SATA 6Gbps支持更为灵活,比如USB 3.0多可以支持6个、SATA 6Gbps多可以拥有6个。但这是有条件的,因为Lynx Point一共有18条PCI-E 2.0通道,其中5、6两条通道可以根据需要分配为USB 3.0或者PCI-E 2.0,13、14两条通道也可以分配给SATA 6Gbps或者PCI-E 2.0。换句话来说,Lynx Point的PCI-E通道有4条可以灵活配置,既可以作为USB 3.0或者SATA 6Gbps,又可以作为PCI-E存在。这让厂商设计和用户选择余地更广,可以根据需求来搭配是要更多的USB、SATA还是PCI-E接口。

其次则是存储方面的进步。Lynx Point支持Fast Synch Streaming(快速同步流)、UEFI快速启动以及Lake Tiny。快速同步流主要用于提升I/O同步速度,比较有趣的是Lake Tiny,这项技术主要是根据功耗和负载情况来配置I/O接口,有助于提高SSD的性能。英特尔的数据表示,在使用了Lake Tiny后,SSD的突发数据流会提升到220MB/s,远远高于未使用Lake Tiny时高大约157B/s的速度。高突发数据读取速度有助于降低系统响应时间,提高系统反应速度。

在型号方面,Lake Tiny在消费级市场方面分为Z87、H87和H81三款芯片组,商务市场则分出了Q87、Q85和B85等产品。消费级市场的产品是用户为关注的产品。其中Z87支持把CPU提供的PCI-E 3.0×16拆分为两条PCI-E 3.0 x8或者一条PCI-E 3.0 x8和两条PCI-E 3.0 x4,也支持CPU超频;H87则只支持将CPU提供的PCI-E 3.0 x16拆分为两条PCI-E 3.0 x8,不支持超频;H81既不支持拆分PCI-E通道也不支持超频。其他方面三款芯片组差距比较小,市场划分情况也类似目前的Z77、H77和Z71的情形。

| 全新的8系列芯片组规格表 | |||

| 规格 | Z87 | H87 | H81 |

| 处理器接口 | LGA1150 | LGA1150 | LGA1150 |

| 图形接口支持 | 1×16或者2×8 或者1×8+2×4 |

1×16或者2×8 | 1×16 |

| 英特尔RES 12 | 支持 | 支持 | 支持 |

| Lake Tiny | 支持 | 不支持 | 不支持 |

| 英特尔Smart Response Techonlogy | 支持 | 支持 | 不支持 |

| USB(USB 3.0) | 14(4) | 14(4) | 10(2) |

| SATA(SATA 6Gbps多) | 6(6) | 6(6) | 4(2) |

| PCI-E 2.0 | 8 | 8 | 6 |

| CPU超频支持 | 支持 | 不支持 | 不支持 |

压路机,开拓新局面?

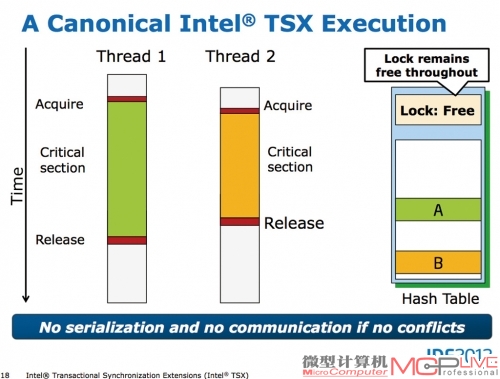

接下来,我们来看看AMD方面的变化。推土机架构是自K8以来AMD所进行的架构设计中变革大的一次,尽管解决了先前K10核心中存在的一些问题,也跟进英特尔的步伐加入了宏指令融合等技术,但市场表现仍然不算很好。在AMD规划的路线图上,推土机之后还有打桩机、压路机与挖掘机三次架构调整。其中压路机的初始设计目标是提高并行性。但是计划赶不上变化,推土机与打桩机连续被压制,AMD的设计重心已经和路线图上强调的部分有了微妙的不同。下面,就让我们从AMD首席技术官Mark Papermaster在Hot Chips 2012年会上的主题演讲中所透露出的信息,对压路机的架构进行分析。他的演说主要集中在三个方面:流水线前端、单核心执行效率提升,以及改进能耗效率。一个本来要继续强化并行性能的架构却将一部分精力花在了单核心效率上,这让我们对压路机的前景更加迷惑,AMD究竟改动了什么?

流水线前端优化

首先来看指令读取。AMD加大了指令缓存的大小,并且使用了更加积极的指令预读取策略,指令向执行单元的交付效率也有所提高。据传,推土机架构的基本流水线长度略高于2 0级,这种长流水的设计能够帮助推土机推高主频,但是也增加了总体的执行延迟,更加大了分支预测失败的损失。为了弥补这个缺陷,推土机当中设置了一个与指令读取分离的多级分支预测器,期望以此减少流水线停顿。压路机架构在此基础上进一步加大了分支目标缓冲区的大小,期望以此提升分支预测的准确率。据AMD内部的仿真测试结果显示,压路机的分支预测失败率降低了20%。

此前推土机架构引发讨论的另一个问题是它的指令解码器共享设计,坊间传闻这是限制推土机架构执行效率的一大败笔。让我们先来看看竞争对手英特尔,它早在2006年的Core架构上就大胆引入了3组简单指令解码器+1组复杂指令解码器的设计,理想状况下每个时钟周期能够给每个处理核心提供四条已经解码完毕的待处理指令。而推土机的指令解码器与之相比则缩水一半,虽然每个推土机模块当中被配置了四个指令解码器,但是却有两个处理核心。于是有人担心,这种缩水的指令解码器能否以足够快的速度去解码指令?

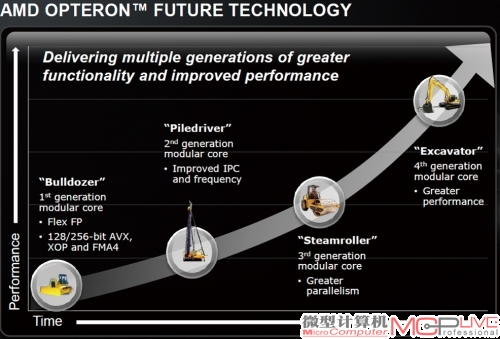

答案是在大多数情况下不会,只有在一些对每时钟周期执行指令数有较高要求的多线程应用下,这种两个核心共享四个指令解码器的设计才会轻微地影响性能。性能略微降低的代价带来的好处是执行解码器数量的降低以及芯片复杂度的降低。x86不同于ARM,它是一种复杂指令集,其指令解码器设计比ARM的精简指令集要复杂很多,也会消耗更多功耗。因此AMD削减推土机模块指令解码器数量的决策是一个牺牲性能换取低功耗的权衡之计。但是现在,AMD希望能提升单核心的执行能力,提高指令解码的速度,于是这一权衡已经不再成立,压路机也变成了每核心四路指令解码器的设计,这样一来一个推土机模块内就有了可以并行工作的八个指令解码器。上述改进加在一起让压路机在AMD内部仿真测试中得以将每周期执行指令数提升30%。

单核心执行效率提升

与指令读取、解码上的改进相呼应,压路机在指令调度方面也有所变化。早在上世纪60年代,当时构筑超级计算机体系结构的架构师们就已经意识到,程序的指令不必按照顺序执行,在保持逻辑顺序的情况下打乱指令的执行次序,将后面不相关的指令提前执行可以获得相当不错的性能提升。从1995年开始,这种原先应用在超级计算机上的乱序执行技术被英特尔首先引入到微处理器Pentium Pro中,从而飞入寻常百姓家。如何在指令与指令之间既保持原有逻辑顺序,又要进行聪明的调度来加速执行,是一门并不简单的学问,压路机中为了方便进行调度增加了更多的寄存器,经过改良后的整数指令调度效率提高了5%~10%,这意味着执行单元停顿的几率更少。上一个部分中提到,为了获取性能的提升,AMD将指令解码器的数量加倍,这就导致了芯片面积的增大(意味着成本提高)和功耗的增加。为了抵消这个部分的影响,压路机的其余部分就必须作出权衡。MMX执行单元和FMAC执行——单元现在共享一部分执行部件_这是什么意思呢?

让我们回忆一下手算乘除法。乘除法在手算过程中会进行一系列的加减法,在处理器当中也是一样,只不过加减法被统一到加法器上运行。如果我们仿照乘除法的手算过程来设计乘法执行单元和除法执行单元,就会发现乘法和除法都需要用到加法器。如果我们在乘法和除法两个执行单元中都配备独立的加法器,那么一个乘法操作就可以与另一个除法操作并行执行,但是劣势在于多出的一个加法器抬高了芯片面积和功耗。与此相对的是,如果我们只设计一个加法器,然后让乘除法单元共享它,性能会受到损失,但是芯片面积和功耗则可以节省下来。AMD在MMX单元和FMAC单元上进行的改动与此类似,但这是一个精巧复杂的权衡,AMD的工程师们仔细拆分了MMX和FMAC指令的执行过程,保证这两种指令不可能同时用到那部分共享的硬件,这使得它在保证一定的芯片面积以及能耗的同时,性能不会受到影响。

除此之外,压路机还进行了一些调整,例如Load指令的压缩能更有效率地利用寄存器空间,改进了Store-to-Load的数据旁路设计,这些改进加在一起使得压路机的单核心执行效率有所提高。

存储器体系的改进

在推土机的架构中,每个模块共享一个64KB大小的两路组关联一级指令缓存,模块内的每个核心单独使用一路(在《微型计算机》2012年7月上刊的《剑指低端独显 Intel Ivy Bridge GPU图形架构解析》一文中,我们介绍过组关联缓存的设计利弊,读者可参阅相关内容)。每个核心单独使用一路的设计意味着这个组关联缓存蜕变成为事实上的全相连缓存,全相连缓存完全抹消了由地址冲突引来的缓存缺失,但代价是需要附加大量的比较器,引入更大的访问延迟。为了弥补这一点,推土机使用组内预测技术来预测每次访问缓存时会检索的一组寄存器,在理想状况下90%以上的访问可以准确预测,只需直接把这组数据取出即可,不用检索整个缓存,从而缩短延迟并降低功耗。这是一箭双雕的聪明设计,但是无法补足每个核心指令缓存大小相比上一代有所减小的缺憾。为此压路机重新加大了一级指令缓存,而容量加大之后一级指令缓存的缺失率降低了30%。但目前AMD仍然没有透露压路机一级指令缓存具体的大小,也没有数据缓存大小的资料,因此数据缓存的部分是否有所改变还未可知。

压路机的二级缓存也有较大的变化,终于支持以四分之一缓存大小为步长的动态增减。在对一个大容量缓存进行检索时,功耗是比较大的,此外二级缓存在推土机架构内占有的漏电流份额也不容忽视,在计算负载比较低的时候关闭一部分二级缓存能够有效节省功耗,AMD认为这对于一些移动终端上的常见应用,例如视频回放(对二级缓存的大小要求不高),可以带来更佳的续航能力。

另一项跟进英特尔步伐的改变是uop缓存。uop指代“微指令”,由于x86指令集指令格式不统一,给流水线设计带来了很大难度,因此当下x86处理器家族内部大多数成员在处理x86指令之前会先将它拆分转换为比较简单的精简指令,随后为这些精简指令设计执行流水线。uop缓存存储的就是这些经过转换的指令。我们之前反复提及,x86指令集的复杂性导致了硬件底层解码器设计的复杂和高功耗,如果需要读取的指令一直出现在uop缓存当中,芯片就能够暂时关闭指令解码器以达到节省功耗的目的。

这种uop缓存设计在Sandy Bridge上就已经存在,AMD算是扮演了一个跟进者的角色,但是称呼不同,AMD将之称为uop队列。同时AMD没有透露uop队列的大小,它能容纳多少解码完毕的微指令还是个未知数。

Haswell是新的期待?压路机能否冲出困局?

英特尔方面,Haswell的CPU部分架构改进并不大,除了新加入的指令集和扩展外(实际提升可能短期内也看不出任何效果),同频率性能提升非常有限,应该在15%左右;图形核心方面,Haswell的GT3应该有比较明显的改进,GT1和GT2的3D性能改进则并不大,距离目前入门级独立显卡仍然有较大差距;Haswell搭配的芯片组方面,除了USB 3.0和SATA 6Gbps外,其余的部分亮点也不是很多,也基本维持了7系列芯片组的市场格局。总体而言,对Haswell的评价,只能说是“饱含期待”。具体情况如何,还得等产品正式发布后才能知晓。

相比英特尔的“ 淡定”,目前CPU产品整体处于劣势的AMD就需要奋起直追了。但从已有的资料来看,压路机在架构方面的变动幅度并不是革命性的。比较乐观的猜测是,AMD的确打算从推土机开始设计一个全新架构,并在随后的几代(打桩机、压路机)里逐步吸收经验,改进缺陷,直至2014年挖掘机架构时再与Haswell一决高下。

这么一来,变动幅度不大的压路机就很可能只是应对Ivy Bridge EX/EP的一个过渡产品。在今年年初召开的财务分析师会议上,AMD已经释放出了再明显不过的战略转型信号。AMD已经很清楚地意识到了移动计算时代的来临,并透露出转向移动市场的愿望,但是资源不足的AMD现在大部分投入仍然是在传统PC市场。总体而言,无论是Haswell还是压路机,都不属于革命性、大幅革新的产品。这主要是两家厂商既定的产品策略、DIY大环境的疲软造成的,毕竟现在离PC大发展、K7和Pentium 4激烈竞争的时代,已经太远太远了。总体而言,目前英特尔占据了CPU的市场的主导优势,AMD则在不停地追赶。在下一代新产品上,我们估计英特尔凭借Haswell仍然会摘得桂冠,当然,至于产品的具体性能,双方的性能水准究竟到了什么地步,我们拭目以待。