DDR4内存全景解析

从SDRAM到DDR、再到DDR2、再到目前的DDR3,每一代内存都要横跨多代PC平台。当前主流的DDR3内存规范于2007年6月由JEDEC确定,经过长时间的发展,DDR3已经彻底取代了前代产品DDR2,成为市场主流。在5年后的2012年下半年,JEDEC又发布了新的DDR4规范,DDR4也将像DDR3取代DDR2那样,慢慢走入我们的PC,成为未来PC的主流内存规范。那么DDR4有哪些优异特性呢?它和当前主流的DDR3又有什么不同呢?今天本文就将为你揭示其中的奥秘。

内存算是目前PC中没有竞争性的部件。内存和显卡、CPU等有充分竞争的产品不同,业内组织JEDEC是目前PC内存规范的唯一制定厂商。JEDEC的内存规范极其详尽甚至事无巨细,包括芯片设计、PCB层数、频率等重要参数,各家内存厂商几乎没有太多的技术发挥空间。因此内存无论是发展速度还是产品本身的规格、技术,都一直处于JEDEC的“强力控制”之下。在DDR3内存还未全面成熟之时,JEDEC就开始考虑下一代DDR4内存的规范情况,并在2010年就公布了部分DDR4的内存资料,终在2012年下半年发布了DDR4内存的白皮书,并有部分内存厂商进入了DDR4内存的试产阶段。

变弯了——DDR4的硬件外观改进

对大部分消费者来说,内存的技术升级是看不到也摸不着的,但是内存外观的变化却是实实在在的。DDR4相比DDR3,在外观上做出了很多改进。

首先,DDR4内存的金手指呈弯曲状。在外观上,传统内存的金手指都是平直的,没有任何弧度。这样的设计在生产和加工时比较方便。从结构来看,内存插入插槽后,除了依靠金属弹片和本身所带来的摩擦力固定外,插槽上还有两个卡口将内存卡紧。因此内存插槽的结构稳定性极为优秀,在实际使用中,全部平直的内存金手指插入内存插槽后,受到的摩擦力较大,因此内存存在难以拔出和难以插入的情况—甚至优秀得有点“过分”,这也导致内存的易用性表现存在一定的瑕疵。

为了解决这个问题,DDR4将内存下部设计为中间稍突出、边缘收矮的形状。在中央的高点和两端的低点以平滑曲线过渡。这样的设计既可以保证DDR4内存的金手指和内存插槽触点有足够的接触面,信号传输稳定无虞,又可以让中间凸起的部分和内存插槽产生足够的摩擦力稳定内存。唯一的问题在于圆弧形的设计增加了PCB加工的难度,在DDR4生产的早期有可能影响产品的价格和产量。

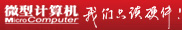

其次,DDR4内存的金手指本身设计有较明显变化。金手指中间的“缺口”也就是防呆口的位置相比DDR3更为靠近中央。在金手指触点数量方面,普通DDR4内存有284个,比DDR3的240个要多,每一个触点的间距从1毫米缩减到0.85毫米,因此长度基本不变。笔记本电脑内存上使用的SO-DIMM DDR4内存有256个触点,触点间距从0.6毫米缩减到了0.5毫米,长度相比触点只有204个SO-DIMM DDR3内存也没有太大的变化。

第三,标准尺寸的DDR4内存在PCB、长度和高度上,也为未来的发展做出了一定调整。由于DDR4芯片封装方式的改变以及高密度、大容量的需要,因此DDR4的PCB层数相比DDR3更多,PCB的厚度也略微增加了0.2毫米。至于在长度和高度上,为了在PCB上容纳双层芯片,因此高度略有增高,长和宽分别增加了0.9毫米和1毫米,达到了68.6毫米长和31.25毫米高。不过仅仅从外观看,不经过仔细对比的话,是不会发现DDR4和DDR3在长宽高上太过明显的区别的。因此DDR4依旧可以使用DDR3的包装材料,这为厂商节约了不少的费用。

一切以速度为核心—DDR4新技术全面看

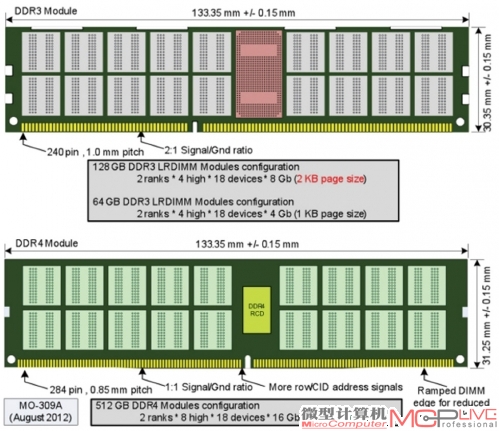

内存发展的核心目标就是不断提升速度。DDR4需要在预取数没有改变的情况下,将等效频率从DDR4 1600起,短期内提升至DDR4 3200,未来会进一步发展到DDR4 4266及以上。当然,从目前来看,DDR4 1600相比DDR3 1600来说,数据并不太好看,这是因为DDR4标准制定比较早,当时没有预计到DDR3会如此迅速的发展到DDR3 1600乃至DDR3 1800和DDR3 2133,因此DDR4起点似乎有点低了。不过DDR3发展至DDR31866以上时,良率严重下降,功耗变高,进一步提升频率变得极为困难。DDR4需要彻底改变这种情况,让频率上升变得更容易。在工艺一定的情况下,频率上升带来的问题也很麻烦,主要是温度变高、工作稳定性降低、信号传输稳定性变差等。这些都是DDR4在高频率运作时需要解决的问题。

目前DDR4成功使用了很多新技术来保证高频率下的稳定性,比如TCSE、TCAR等,此外,DDR4采用了全新的点对点总线,内存设计上使用了3DS技术,随着工艺的进一步进化,DDR4将能够运行在更高的频率上,为未来的计算释放出强大的数据带宽。

内部的“ 多通道”—Bank Group

在DDR4之前所有的DDR内存中,都没有使用如此大胆的创新设计。DDR在发展的过程中,一直都以增加数据预取值为主要的性能提升手段。但到了DDR4时代,数据预取的增加变得更为困难,继承于GDDR5的Bank Group设计就应运而生了

为了说清楚Bank Group的意义,还得说一些题外话。比如内存的I/O速度和芯片存取速度(实际上这样描述并不足够严谨,但分开来说的确更容易理解)。

将内存拆开来看,实际上内存就是一个自带运输能力的仓库。仓库本身的存储能力和仓库的运输能力是两码事。先定义仓库的存储能力,包含两个方面:存储容量和存取速度;仓库的运输能力则定义为如何尽可能快地将数据传输到外部。

如果要建立一个高速的仓库,需要同时满足两个方面的条件:首先是仓库本身将货物从库房中存取的速度要足够快,其次是这些货物可以很快地运输到外部。在DDR上,使用了2bit预取,相当于库房每次可以存取2件货物,同时DDR数据总线可以同时存或者取货物(SDRAM同时间内只能发或者收,因此相对速度慢了一倍)。在DDR3上,仓库运输能力随着频率而大幅度提升,以DDR31600为例,仓库的运输速度(I/O总线时钟频率)达到了800MHz,每个时钟周期可以同时收发数据,恰好满足仓库本身200MHz、8n预取带来的1600MT/s数据流量。

继续提升仓库的存取速度遇到了难题,预取在已经达到8 n的情况下难以进一步提升。业内专家想出了新的办法:针对目前一个仓库只配备一个内部存取中心的做法,如果将一个大仓库分拆开来,分为两个或者四个小仓库,为每个小仓库都配备一个内部存取中心的话,会怎么样?当数据来临时,会被分为两份或者四份分别存入这四个小仓库,这相当于直接将速度提升了两倍到四倍之多。

GDDR 5就是这样做的。它在内部设计了Bank Group架构,每个Bank Group可以独立读写数据,这样一来内部的数据吞吐量大幅度提升,可以同时读取大量的数据,内存的等效频率在这种设置下也得到巨大的提升。

如果内存内部设计了两个独立的Bank Group,相当于每次操作16bit的数据,变相地将内存预取值提高到了16n,如果是四个独立的Bank Group,则变相的预取值提高到了32n。与之而来的代价是内存内部设计上的复杂性增加,但好处也同样明显,那就是延迟不会有太明显的提高。因为这样的技术只是将内存内部的结构做出优化设计,并没有直接提升根本的数据预取值,相当于组建了内存内部的多通道,预取值理论上和之前的设计完全一样。

事情还没结束,问题又来了:仓库本身在拆分后,仓库数据存储能力大大提高,那么运输速度呢?如果I/O总线的速度不能大幅度提升,空有仓库的运转能力但运输跟不上也是一场空。在GDDR 4上,虽然提升了预取值到8n,但是I/O总线没有彻底更新,和GDDR 3的总线相当,因此终存取速度没有什么革命性的变化,还带来了高频率和高功耗的困扰,终究功亏一篑。GDDR 5在这方面做得很出色,一条路不够就修两条,GDDR5设计了两条I/O总线,每时钟周期可以同时收发4次数据,双I/O总线带来了GDDR 5传输能力和等效频率的大幅提升。

言归正传,DDR4是怎样做的呢?DDR4也采用了Bank Group技术,内部可以支持2个或者4个Group,能够同时对这些Group进行操作。就像上文描述的那样,Bank Group带来了DDR4内部数据传输能力的大幅度提升,让DDR4在物理频率没有太大提升的情况下能大幅度提升数据存取能力。在I/O总线的配置上,目前暂时没有资料说明DDR4是否使用了类似GDDR5的双总线传输,不过很显然的一点是,DDR4频率提升的空间很大,如果没有解决I/O总线的传输问题,肯定不会有如此幅度的性能提升。

总的来看,凭借Bank Group的设计,DDR4获得了非常大的发展空间,这是技术型产品需要长期发展不可或缺的重要内容。只有在未来有持续的发展空间,DDR4才能在3~5年中对未来计算带宽提供足够支持。