SOFT MACHINES VISC CPU架构初步解析

近年来多核心CPU的发展势头非常迅猛,在消费级PC市场上4~8核心处理器产品已成为很常见的产品,同时再加上像超线程这类新技术的出现与帮助,使得普通用户就能享受到8~16 CPU线程同时运算的快感,处理器的多线程计算性能得到极大的提升。然而另一方面则是CPU单线程性能长时间的“毫无作为”,虽然CPU单线程性能也在进步,但与多线程性能的进步幅度相比则可谓不值一提。同时很多消费级软件对CPU单线程的依赖,如大量游戏、PhotoShop图片处理等也使得用户深感CPU单线程性能的不足。为此,广大用户非常渴求CPU的单线程性能也能获得大幅升级,甚至在去年很多人为Skylake处理器“幻想”出了一个可以联合多个CPU线程,用于执行单一任务的“逆向超线程”新技术。

而令人兴奋的是,从本刊在2015年10月下刊《解析CPU逆向超线程技术可行性》一文中的分析,可以看到要想大幅提升CPU单线程性能并非不可能,逆向超线程技术并非完全虚构,很多科技人员早就在从事这项研究。而近期一家名为Soft Machines的公司更拿出了切实的解决方案,号称能实现IPC倍增式的提高,接下来就让我们走进CPU单线程性能的提升利器一VISC CPU架构。

不简单的“新人” Soft Machines和VISC

IPC倍增式的提高,这样的豪言壮语究竟出自何方神圣?可能很多人是头一次听说Soft Machines公司的大名。这是一家位于硅谷的创业公司,在2006、2007年左右成立。一般来说初创阶段的公司会刻意在相当长的一段时间里保持低调,也就是所谓的“秘密阶段”(Stealth mode),在具有一定成果了之后,突然释放出爆炸性消息来吸引关注,当年设计超长指令字结构+动态二进制翻译的全美达公司也曾玩过这个手段,其公司网站曾在两年半的时间里面只挂着一句话“网页还没建好”(This web page is not yet here.),然而私下里却签署了超过2000份保密协议来确保公司的技术和商业目标不被泄露。从这点上来说,Soft Machines选择了和当年全美达类似的路线,直到2014年才脱离“秘密创业阶段”(Stealth mode),走向前台。这家公司迄今为止收到了一亿多美元的投资,投资者包括三星、GlobalFoundries、AMD,拥有75项专利,大约250名雇员,包括前Intel、AMD、高通公司的工程师。Soft Machines试图通过推动CPU单线程性能的增长,使用全新的结构(被称为VISC)来达到IPC倍增。

Soft Machines公布的第一代VISC架构处理器产品原型照片

这一目标不可不谓宏大,加之先前的刻意保密形成的助推,Soft Machines公司刚刚走入公众视线就是大红大紫的状态,特别是IPC倍增的高调声明尤为吸引眼球。日前该公司召开了一次媒体发布会,公布了一些可供玩味的资料,使得我们可以窥探其结构内部的细节、初步分析该技术的前景。

Tips:动态翻译代码缓存和全美达的代码优化流程

因为每一条指令执行前都要经过翻译,但是自我修改代码(也就是代码会修改代码自身)的情况很少,所以可以把已经翻译完的代码保存在一个缓存里面,以供下次使用。除此之外,因为全美达的代码优化工作主要在软件上完成,因此对于总是执行、经常执行、不太执行、偶尔执行的代码,全美达设置了四种不同的优化阈值。对于总是执行的代码,花费多的时间做深的优化,虽然时间花费多,但是执行起来以后可以补回优化浪费的时间;对于执行很少的代码,就不做优化或者只花费少量时间做很浅的优化,以此来降低软件层面的开销。这两种优化技术都被NVIDIA吸收,应用在丹佛计划的自研核心上,往期的《微型计算机》也做过专门解析。

变化不大 指令翻译依赖软件层

让我们先来分析一下Soft Machines提出VISC的技术背景,一个要让IPC倍增的结构应该长成什么样子?这是不是在吹牛?

无数历史经验表明,一个全新的结构如果想要获取软件层面的支持,修改指令集层面是需要慎之又慎的,指令集保持不变才能大限度地兼容现有的种种软件,包括操作系统和普通应用程序。所以在VISC的结构框架里,所有的软件线程需要原封不动地在整个系统栈中向下传递,这是Soft Machines唯一的选择,不出意外地,我们终看到Soft Machines设计的VISC也的确是原封不动地接受上层软件的代码。但是这样一来就限制了后继优化的发挥,如何从这些原封不动的软件线程中抽取指令级并行度呢?

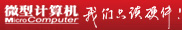

VISC执行框架

VISC的软件架构,图中出现的Dynamic Optimization动态优化有可能是借鉴了全美达、NVIDIA丹佛的设计。

包括全美达在内的一批上世纪90年代的先驱者们已经探索出一条路线:指令翻译层。在VISC的执行框架中,既有指令集的指令会被一个中间翻译层翻译为VISC硬件特有的硬件指令格式。目前Soft Machines确认支持将两种上层指令集翻译成VISC专属的硬件格式,其中之一是ARMv8,另外一个坊间传闻可能是x86,但是Soft Machines未予确认。这个软件翻译层会带来多大的翻译开销是一个对性能至关重要的问题,但此次并未在公开资料中提及。

这个中间翻译层和Intel的CISC x86指令转RISC uops指令格式不同,Intel的翻译是完全基于硬件完成,优势是翻译速度,缺点是丧失了灵活性。也就是说如果翻译部分需要更新,就需要修改硬件,只能等待下一代芯片,而全美达和VISC都选择把翻译层做在软件上,好处是降低了设计复杂度,允许软件层面的补丁来持续更新翻译部分,坏处是性能会受到影响,毕竟每一条指令都要经过翻译。为了减少这一负面影响,全美达使用了两种技术,也就是动态翻译代码缓存和分层的反馈式代码优化来解决这个问题,这项技术后来也被NVIDIA做进了丹佛计划中的自研核心上。Soft Machines在这个问题上则处理得比较含糊,在VISC的媒体通气会上公布的一页PPT上出现了与全美达和丹佛类似的Dynamic optimization动态优化流程,但是没有更进一步披露的情况下,也无法确认这个设计是否暗示着采用了与全美达和丹佛类似的流程。

但是可以确定的是,即便这个动态优化流程存在,也没有设计得如同全美达和丹佛那样激进。据外媒报道,Soft Machines曾表态不应该在软件层面上投入过多的优化精力来追求性能。这是一句非常耐人寻味的话。为什么Soft Machines没有选择和以往的几个设计一样,在软件层面做大量的优化来追求性能呢?这就是VISC结构有意思的地方:Soft Machines虽然吸收了前辈们的经验引入了软件翻译层,但是却不在软件层面上做性能优化,它的秘密武器藏在硬件微结构上。

实现指令切分与核心融合 VISC核心微结构解析

在Soft Machines设计的这种执行框架下,软件翻译层翻译完的指令会通过一个全局共享的硬件前端(Global Front End),指令序列会在这里被切分成多个虚拟硬件线程,然后继续递交给多个执行核心。

VISC的执行框架与核心流水线

指令序列如何切分呢?我们可以看看这个直观的例子,以下四条指令看似是只能逐一执行的单线程任务,但通过指令切分,VISC结构可以让它实现部分并行运算。

1.寄存器1=寄存器2+寄存器 3

2.寄存器4=寄存器2+寄存器 4

3.将地址01的值装入寄存器1

4.寄存器1=寄存器1+寄存器4

首先在允许寄存器重命名的情况下,前三条指令可以单独开辟一个硬件线程来执行。我们来分析一下为什么:第一条指令之前没有任何指令,肯定可以独立开来并行执行;第二条指令只需要读取寄存器2的值,只要寄存器堆的读写端口足够多,同时读一个寄存器的值没有问题,因此也可以独立开来并行执行,第三条指令需要对寄存器1做写操作,看上去与指令1有冲突,但是通过寄存器重命名可以将第一条指令的寄存器1和第三条指令的寄存器1分别重命名成两个不同的物理寄存器,因此也可以独立开来并行执行。但是第四条指令需要用到寄存器1的新值,也就是刚刚从地址01装载上来的值,这是一个真实的数据相关关系,不能通过寄存器重命名变换来消除掉,所以第四条指令不再能够并行。

这个例子演示了简单的一个硬件指令切分,从上个世纪60年代开始,业界就在苦苦追求能够进行全程序范围的指令分析,从而设计出并行度达到理论大值的架构,这种架构被称为数据流架构(Dataflow architecture)。但是截至目前为止,数据流架构仍然没有在CPU这个层面迈向实用化,事实上,传统硬件乱序多发射也正是这样分析指令相关性、抽取指令级并行度的,但是硬件受限于规模,只能在有限的范围内做这样的相关性分析,这个范围被称为乱序执行窗口的大小。在Intel的新一代的Skylake微结构上,这个窗口大小约为200多条指令,也就是说,即便考虑进指令融合,目前的硬件分析处理极限也就是在200~300多条指令的范围上。因此,现在广泛流行的硬件乱序多发射实际上是一个经过弱化、分析范围受到极大限制的数据流架构。基于软件的分析可以克服硬件分析范围不足的问题,目前的软件分析可以借助自身的灵活性去分析几乎无穷大范围的指令序列,相关的一些优化也做进了标准的编译优化流程里,只是分析速度会比硬件有数量级程度的落后。

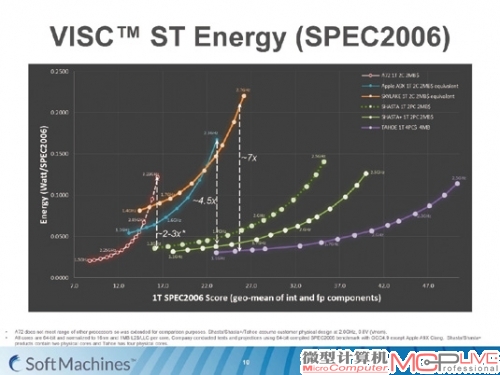

VISC核心流水线细节

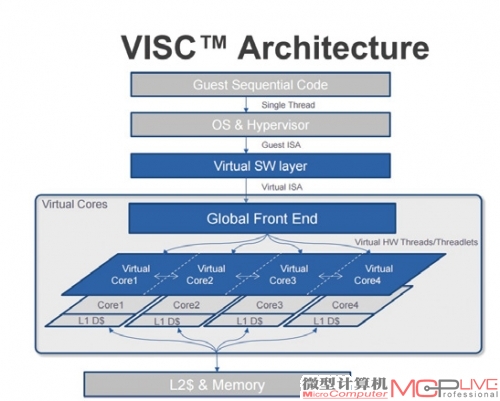

VISC在SPEC2006的测试成绩,SHASTA和TAHOE分别是VISC的第一代和第二代设计的代号,1T代表1个软件线程,2PC代表两个物理核心(Physical Core),除了VISC以外,其余芯片虽然有多核设计,但是只能把一个软件线程放在一个核心上执行。

那么VISC的这个解决方案厉害的部分在哪里呢?注意框架图中的全局共享前端部件,它画在Virtual Cores的框架内部,也就是说它同样是通过硬件进行指令分析。这个硬件分析流程能做到多快的分析速度,能分析多大范围的指令,在公开资料中都没有披露,但笔者仍为此感到兴奋,因为这个设计有着暗含的一层意思:如果VISC的设计方案,没有信心在指令级并行度的抽取范围上超越传统的硬件乱序多发射,他们就不会选择把这个关键部件做在硬件上,否则就失去了创新技术的意义。可以乐观地估计,VISC的设计将可以在指令级并行度的抽取能力上大大超越传统框架下的乱序多发射,可能更加逼近数据流架构的完全形态,亦或者是业界长期困扰无法解决的线程级推测执行的硬件实现版。无论这个设计方案后能否达到设计预期,都是一个非常值得钦佩,也非常值得关注的大胆尝试。

除了硬件切分以外,这个核心微结构里面还存在着另一个亮点。在全局共享前端切分了执行序列以后,被分隔开的各个独立执行线程可以被动态地分配给下面的多个物理执行核心,分配粒度达到了几个时钟周期的级别,并且含糊地提到了可以动态地追踪各个核心中的数据流向。这是令笔者感到兴奋的第二个亮点:业界一直在探索的另外一个方向,核心融合,在VISC的微结构中现身了。“核心融合”实际上就是坊间流传很久的“逆向超线程”技术,将多个核心的执行资源合并成一个来使用,也是VISC结构的重点。在往期的《微型计算机》也曾介绍过,核心融合技术的一大难题是如何实现各个核心间的低延迟通信。在上面的那个指令切分例子中,如果我们把前三条指令放到三个不同核心上执行,到了第四条指令的时候,就要把负责指令1的核心和负责指令3的核心中产生的新数据传递给负责指令4的核心,如果低延迟通信不能实现,逆向超线程实际上也就是镜中花水中月。Soft Machines宣称可以在几个周期的延迟下通过寄存器堆和一级缓存交换数据,尤为令人震惊。

另一个值得关注的问题是推测执行(Speculative Execution)。现代高性能微结构大量地使用推测执行来提高性能,例如往期介绍过的访存地址反别名的推测性分析,以及分支预测。如何进行精准的推测,以及如何从错误推测中快速回退也是非常重要的高性能设计技术。Soft Machines披露,VISC结构可以在个位数的执行周期中从错误预测的分支中回退,但是除此以外没有披露其他有用的信息。从核心内部的流水线上来看,分派(Dispatch)、寄存器读与执行和传统流水线区别并不大,但是整个流水线的前半段才是VISC的不同之处。硬件虚拟线程的形成(formation)、执行资源的分配(allocation)、调度(scheduling)花了9-12个周期的时间,对比传统的硬件乱序多发射流水线,指令从取出到解码、重命名、推入保留站也需要大约十个时钟周期左右,从流水线深度上来说VISC与传统解决方案可能是互相持平。Soft Machines认为自己的设计应该算是短流水,对此笔者不敢苟同,在流水线深度上来说VISC结构并不占优势。硬件虚拟线程的处理也是颇为核心的要素,可惜的是Soft Machines到目前为止也没有公布更多的信息,使得外界的判断多半流于猜测。虽然许多关键细节缺失,但从目前已知的信息来看,VISC的这个设计基本已经靠拢了大家想象中的“逆向超线程”,由一个全局共享前端对一个单线程的指令切分成多个虚拟硬件线程,然后多核心的执行资源互相协作执行,允许低延迟地相互传递数据,可以说“逆向超线程”是描述这种设计的好解释。

可信度不高 疑云重重的测试数据

从设计框架上来看,VISC确实非常超前,实践了至少两个目前仍处于探索阶段、未见大规模工业化量产的结构设计点,那么它的实测性能如何呢?从VISC开始放出消息到现在,许多人为它宣称的IPC成倍提高感到震惊,后来更是由震惊转而怀疑。Soft Machines于今年向媒体公布了一组测试数据,但是仍未能打消怀疑,反而引来了更多外界的质疑。如上一页右下图,这组数据的横轴是SPEC2006的性能测试分数,纵轴是这个SPEC分数水平背后对应的单位能量消耗。乍看之下,VISC的新设计似乎在性能和能耗上完全碾压了现有乱序多发射设计中的几个代表性样本,但实际上并非如此。这张图被诟病多的一点就是:图中的SPEC2006测试分数不是SPECint也不是SPECfp,而是SPECint和SPECfp的几何平均数,使得其真实性能水平被盖上了一层伪装。

SPECint和SPECfp是SPEC CPU基准测试程序中的两大组件,包括截然不同的一批测试项目,分别统计整数性能和浮点性能。由于整数和浮点测试集的性能特征差别太大,一般来说这两个分数是各自独立计算的。Soft Machines将这两者混合统计是一个明显、不可辨驳的错误,也让外界对VISC产品的性能解读变得更加困难。当年基于超长指令字结构的安腾系列CPU就是在浮点上领先同时代其他硬件的乱序多发射设计,但是整数性能则十分孱弱。笔者怀疑Soft Machines的这个错误是为了掩盖整数性能的落后,而有意为之。

即便忽视了混合SPECint和SPECfp这个严重错误,Soft Machines的测试仍旧如同筛子一样满是疑点和漏洞。Soft Machines声称所有的参测CPU都按照某种“业界标准”把测试分数按照Last-Level-Cache(即处理器的后一级缓存,如普通CPU的三级缓存)1MB大小的设定进行了调整。笔者从未听说过有这个“业界标准”的存在,SPEC测试集中的测试程序有的对Last-Level-Cache极其敏感,如429.mcf,在一定Last-Level-Cache容量范围以内它的执行性能几乎是随着容量呈现线性增长的,也有的如同403.gcc,在不同的Last-Level-Cache大小下性能只有个位数百分点的小幅波动,几乎可以忽略不计。这个“业界标准”就算是真的存在,又要如何去处理这种情况呢?对不同的测试子项进行不同的加权处理吗?

另外,目前Soft Machines已经有了TSMC 28nm工艺生产的第一代产品原型,运行频率为500MHz,可以启动Linux系统,也就是说可以肯定Soft Machines已经脱离了纸面设计的阶段,至少有了可以完整工作的初步原型。但是Soft Machines的所有性能测试都是基于RTL仿真进行的,即便我们大度地假定这个RTL仿真是加入了完整正确时序信息的后仿真、并且忽视后仿真和实际流片之间的差距,这个测试方法也令人难以接受。目前Soft Machines手上只有500MHz的原型,在这个节点上使用简单的插值推算2GHz及其以上性能水平是很危险的做法。主频的跨越式提高往往需要借助结构设计与逻辑的变动,但是这样的变动也同时意味着IPC的值会同时发生变化。具体变动幅度有多大,只有做完了高主频设计、再重新进行测试评估才能知道。Soft Machines认为这样的仿真测试与真实设计之间只会有5%~10%的差距,在没有进一步证据予以佐证的情况下,笔者认为这一点存在不可回避的漏洞。

基于这一份公开数据,Soft Machines的VISC概念和原型系统是无法说服业界的,甚至由于数据的呈现方式上出现了重大错误,不由得让人怀疑这样的数据背后是不是有着某种掩饰性的考量,所以这次的性能披露非但没有说明什么问题,反而是令Soft Machines的公信力蒙受损失。

Tips:SPECint和SPECfp的区别

整数和浮点程序拥有截然不同的性能特征,其中关键的一点就是指令级并行度的富余程度,在过往的模拟器测试上,若采用相同的测试结构参数,整数测试集的指令级并行度上限相比浮点测试集有几倍的差距,因为浮点的指令级并行度上限很高,所以众多尝试发掘指令级并行度的设计往往能在浮点测试中取得较好成绩但是整数测试中表现不佳,这也是现代GPGPU长于并行计算而弱于分支判断的原因。

保持乐观态度 如何看待Soft Machines?

虽然测试数据无法令人信服,结构设计的要点也是存有模糊,但是笔者仍然坚持认为对于Soft Machines以及它的VISC产品抱持宽容态度。为什么呢?这要从微结构的发展历史与目前的行业现状来解释一番。

微结构设计和研发,直观地说,其实非常像是在一片泥泞不堪、布满深坑和陷阱的地域上寻找埋藏的宝藏。在上世纪八九十年代,业界刚刚开始迈过高性能微结构门槛的时候(九十年代初才诞生第一个基于CMOS的多发射设计),可以说整个业界对这片地域是所知不多的,当时的微结构,即便是量产化的工业级设计,背后的实验支持和理论分析都远没有今天这么雄厚,因此带有很强的探索性质。回头翻阅当时的发展历史不难看出,有无数疯狂的概念设计倒在了初步模拟实验的阶段,未能更进一步,颇具代表性的例子就是值预测(Value Prediction)技术的研究。这种技术期望于通过程序执行地址、循环执行次数等信息,在实际计算完成前就预测计算结果,但由于准确率确实不佳,至今未能得到主流认可,投入在这个方向上的大量经费和结构设计专家的人力资源可以说算是掉进坑里了。但是这些投入完全没有任何意义吗?

不尽然。这些不成功的设计有两个作用:其一,明确告诉后人,这里有坑,谨慎绕行;其二,从中可以抽取出有用的实验数据并加以分析,有可能得到意外收获。例如在值预测这个大坑旁边,光笔者所知就有至少两个被证明有价值的矿点:访存地址反别名分析(memory disambiguation)以及循环指令缓存(loop cache)的执行次数预测。

随着时间推移,越来越多的实验数据和理论分析积累,有一个大矿点被系统地发掘出来,其附近地域也被公认为安全地带。这个大矿点就是由上世纪60年代的CDC6600首创,IBM 360/91加强的硬件乱序多发射设计框架。在硬件乱序多发射优势尚不稳固的时候,亦有一批先驱者奔向其他可能的矿区开始试探性采掘,这里面有代表性的例子就是超长指令字(VLIW)结构。而随着Intel Itanium系列的失败,这片矿点就被公认为价值不如硬件乱序多发射,只在少量场合下继续使用。随着越来越多的资源投入到对硬件乱序多发射的开掘,这片矿区的身价进一步水涨船高,终超越了所有其他选择,并且在大多数应用场景下至今仍保持压倒性优势。截止到这个时间点上,硬件乱序多发射框架就变成了事实上的第一选择以及近乎是唯一选择。除了屈指可数的几个异类以外(全美达、NVIDIA丹佛、Intel安腾,IBM Power6),硬件乱序多发射变成了高性能CPU的立足点。脱离这个框架,踩在其他区域尝试探索起步的设计几乎后都宣告失败。只有踩在硬件乱序多发射圈定范围内的设计才能存活,颇有点《切尔诺贝利:晴空》那片辐射变异地带里安全区的味道。

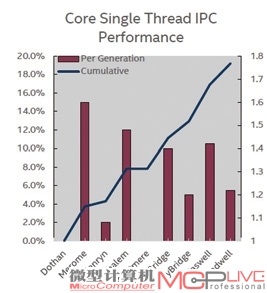

Intel各代CPU核心的IPC增长幅度

从2005年前后开始,硬件乱序多发射的增长潜力开始放缓。从Dothan到Merom到Nehalem到近的Skylake,主体结构基本上没有出现多少变化,性能的增长只是来源于在同一个结构框架下的小幅调优,每年带来10%上下的改进,仅此而已。这片安全区仍然安全,能够保证设计框架的大方向不会出现重大错误,但是宝藏也挖空了。

从这个尺度上来说,在传统硬件乱序多发射框架以外进行探索的这些努力就显得特别珍贵。并不是每个研究机构、公司都有这样的信心去挑战传统硬件乱序多发射框架几十年积累下来的优势,尝试做出一些颠覆性的改变。在这几十年中,偏离硬件乱序多发射框架的“探路者”们其实数目不少,但是做得有声有色、一度曾让人燃起希望的则少之又少。像VISC这样的个例,尽管已经显露出有很大的不靠谱可能性,但是笔者仍然坚持推崇其探索的努力,在挑战传统这件事情上,失败是常态,成功是偶尔。

也有一些外界批评认为,VISC目前的第一代产品原型只能运行在500MHz的频率上,这是否说明其结构设计的流水化存在问题,使得频率暴降?这的确有可能,要让多个物理核心同时追踪较大范围的指令相关性,低频可能是不可避免的,但同时也要看到,作为原型设计推出的东西,而且又是第一代,往往不是以性能为第一设计考量。原型系统的第一目的是测试整个执行框架是否可工作、是否可行,时序只要收敛就好,并不太追求高频率,以原型系统的频率来评判其量产频率是不对的。如果Soft Machines后继的几代系统都只能工作在低频下,才能比较有力地说明其结构流水线确实存在问题。以新结构为卖点的创业公司尤为艰难,当年的全美达公司几乎一直处于烧钱状态,盈利很少,希望Soft Machines能坚持下去。同时笔者也希望Soft Machines如果万一也不幸走到失败地步,能够以更加开放一些的态度提供更加详细的结构设计资料和测试数据,为可能出现的下一个、下一批勇敢闯出安全区的人亮起一座灯塔。