全新英特尔至强E5 v4系列处理器解读

2016年4月1日,英特尔在北京发布了全新的至强 E5-2600 v4家族处理器(简称E5 v4),配备了全新的工艺、全新的架构、更完善的档次划分。那么这一次英特尔在发布会上带来了那些干货?相比2014年9月发布的E5 v3,E5 v4性能提升几何?对于实际的行业用户而言它又带来了哪些好处?就让我们一一为你解读!

随着互联网和移动计算的进一步发展,云以及云代表的产业链在近几年开始呈现爆发的增长态势。无论是国家层面的“互联网+”战略,还是传统产业的互联网转型,再加上各种各样的公众云、私有云、行业云的诞生,云时代下数据的处理、存储、使用成为厂商和用户直面的核心问题。也正是看到了这个变化,英特尔希望借助新的至强 E5-2600 v4,进一步提升性能,加强稳定性,细化功能,让英特尔在云计算时代继续维持绝对的统治力。

更多核心、更多特性——至强 E5-2600 v4特性解读

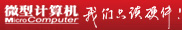

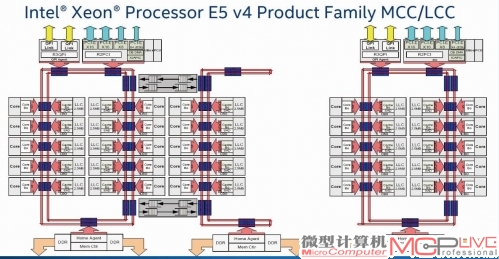

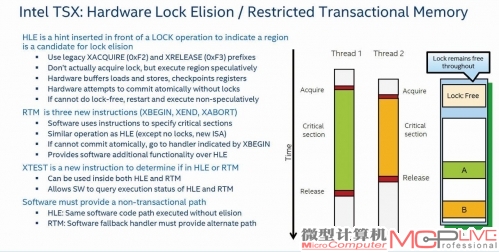

首先,我们先熟悉一下至强 E5-2600 v4家族产品的基本情况。至强 E5-2600 v4家族拥有三款不同的核心配置,分别是高核心数(High Core Count,HCC)、中等核心数(Medium Core Count,MCC)和低核心数(Low Core Count,LCC)。其中高核心数高可配置24个内核(但实际产品只开启了22个)、中等核心数高可配置14个内核、低核心产品高可配置8个内核。TDP等数值随着核心数量和频率等不同配置方案而略有不同。技术方面,相比上代至强 E5-2600 v3系列,至强 E5-2600 v4系列的技术改进主要在换用了全新的Broadwell架构、制造工艺进化至14nm、核心数量从上代的18个提升至大22个、超线程核心也顺理成章增加至44个、缓存容量进一步提升至大55MB、首次加入了对3D堆栈式内存技术的支持,使得大内存支持可达3TB以上。此外,诸如资源直配技术(RDT)、虚拟化增强以及TSX交易同步扩展指令集、增强的安全特性等技术也加强了新产品在新应用环境下的优势。

从工艺角度来看,至强 E5-2600 v4家族全部采用了新的14nm工艺,相比之前的22nm工艺而言,新的工艺线宽更小、能够在有限的面积内容纳更多的晶体管、驱动电压也有一定的降低,更节省电能。正是由于新工艺的使用,至强 E5-2600 v4可容纳的内核数量才从之前的多18个提升到大24个—不过由于细分市场和TDP等问题,英特尔在E5级别的处理器上多只开启了22个核心,只有E7等级的处理器上用户才能得到完整的24个核心,不过此时高TDP也会提升至165W。在应用了新工艺后,高核心数配置下,处理器面积达到了465平方毫米,晶体管数量高达72亿个;中等核心数配置的芯片面积为306平方毫米,晶体管数量为47亿个;低核心数配置的核心面积为236平方毫米,晶体管数量为34亿个。相比上一代18核的至强 E5-2600 v3核心面积高达662平方毫米而言,全新的14nm工艺带来的集成度提升有目共睹。

至强 E5-2600 v4家族基本特性概览及与前代产品的主要规格对比。

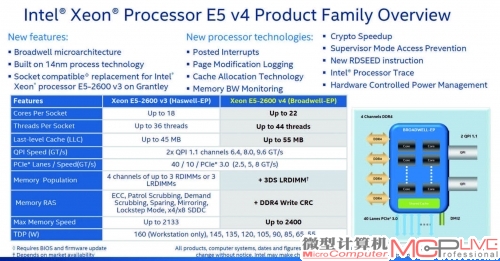

除了性能外,至强 E5-2600 v4还加强了安全功能,包括加密和安全认证方面的功能。

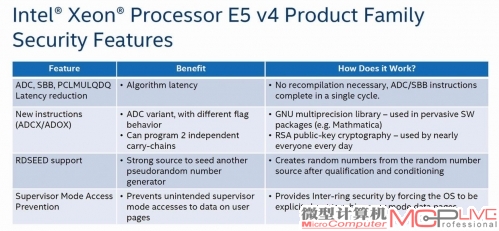

至强 E5-2600 v4家族HCC、MCC和LCC不同的配置情况。

Tick步骤——单核心改进不多

在核心改进方面,由于本次从Haswell-EP进化至Broadwell-EP属于英特尔架构改进中的“微架构不变,制程工艺更新”的步骤,也就是传说中的“Tick”步骤,因此整体核心只是微调,架构方面的改进并不大,包括core和uncore的前端、指令解码、缓存、各种功能单元、总线、接口等,Broadwell-EP都基本维持了和Haswell-EP一样的设计。尤其是从Ivy-Bridge-EP就开始使用、在Haswell-EP上大幅度改善调整的环形总线,在Broadwell-EP上得到了全盘继承。相比之前的Haswell-EP上多挂载18个处理器核心,Broadwell-EP上高可挂载24个处理器核心,其双向、分组环形总线的设计和缓冲器方案,使得英特尔能够在更多核芯的情况下,实现核心资源的有效调配和控制。

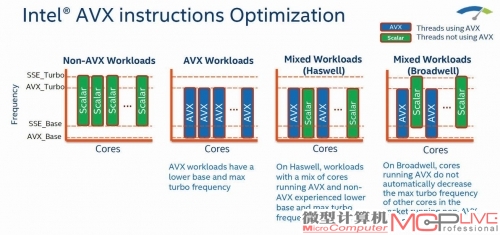

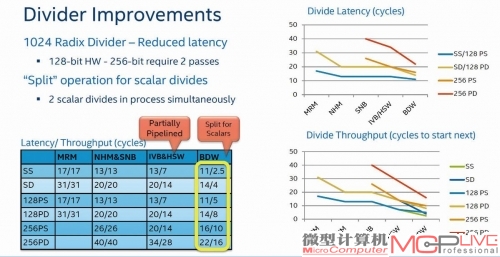

虽然硬件架构基本相同,但这并不意味Broadwell-EP架构没有做出改进。英特尔宣称,相比Haswell-EP, Broadwell-EP的IPC性能略微提升了约5%,其中大的变化发生在调度器和缓冲器上。Broadwell-EP的乱序调度器窗口更大(从60提升至64)、允许更多的指令被重新排队,相应的提高了IPC。此外,L2 TLB也从1K增加至1.5K,减少了地址条目转换失误。在TLB方面,英特尔还增加了一个TLB页面,允许Broadwell-EP同时并行处理内存页。在计算能力方面,Broadwell-EP的浮点能力得到了加强,包括浮点乘法周期从之前的5周期降低至3周期、使用了1024(10bit)分频器等。此外,Broadwell-EP还改进了分支预测单元,从之前的8路提升至10路,在微指令优化方面加强了并行性、减少指令延迟(ADC, CMOV, PCLMULQDQ的指令延迟降低至1uop)、加入了全新指令等。

总的来看,虽然核心架构的改变不总是大幅度的,但每一代英特尔处理器产品在性能上相对于前作都具有优势;配合英特尔比较频繁的核心改进次数,从Nehalem开始,到随后的Sandy Bridge、Ivy Bridge、Haswell再到今天的Broadwell,如果每代的IPC增长都在5%左右的话,数代累积下来整体性能提升是非常可观的。这一次Broadwell-EP是Tick步骤,整体改善并不大,但依旧获得了IPC约5%的提升以及核心数量、频率方面的变化,可想而知下一次Skylake-EP,整体性能有望更进一步增强。

目前Broadwell-EP的TSX功能终于可用了,包括事务型内存等技术都能够正常的为用户提供功能。之前Haswell-EP上,TSX出现了一些BUG,英特尔不得不关闭了这个功能。

Broadwell-EP在IPC上有了一定的提升。

Broadwell-EP进一步加强了AVX性能。

Broadwell-EP在浮点性能和TLB、分支预测上的提升。